📢 업무를 하며 Cortex-R52 Architecture에 대해 알아봐야해서 Armv8-R AArch32를 알아봤어요

Armv8-R AArch32의 등장

2013년 Virtualization 기능을 탑재한 Armv8-R AArch32가 등장 했어요

R 시리즈는 실시간성 보장, 낮은 latency를 요구하는 시스템에서 효율적인 제어를 할 수 있어요

권한 레벨

안전한 시스템 동작을 위해 존재해요

Application은 PL0 권한을 가져 직접적인 시스템 자원 접근에 제한이 있죠

Decreasing privilege ↑

+-------------------+

| Tasks | PL0

+-------------------+

| RTOS | PL1

+-------------------+

| Hypervisor | PL2

+-------------------+

Increasing privilege ↓

Level of privilege: PL0 < PL1 < PL2

- PL0 : Tasks

- PL1 : Guest OS (RTOS)

- PL2 : Hypervisor

각각은 Execption Level의 EL0, EL1, EL2와 대응되는 것 같아요

Virtualization

가상화는 여러 VMs가 같은 물리 머신 위에서 동작하게 해줘요

하나의 프로세서에서 여러 OS를 격리 실행하여 자원 활용률을 높이고 안전성을 확보하기 위해 사용하죠

VM1 VM2

+------------+ +------------+

PL0 | Task | | Task |

+------------+ +------------+

PL1 | RTOS | | RTOS |

+------------+ +------------+

+------------------------------+

PL2 | Hypervisor |

+------------------------------+

PL2(EL2)에서 동작하는 SW인 Hypervisor는 VMs를 스케줄링하고 생성하는 책임을 가져요

Hypervisor는...

- Guest OS(VM, PL1)에서 레지스터 제어를 하면 Trap이 발생하며 Hypervisor(PL2)로 제어권이 넘어가고 동작을 emulation 해요 (Trap and Emulate)

- Stage2 MPU를 통해 hypervisor가 Guest OS의 허용되지 않은 메모리 주소 접근을 막아줘요

- Virtual Interrupt 지원을 통해 Hypervisor가 인터럽트를 각 VM으로 전달 할 수 있게 해줘요 (vGIC)

Memory Protection Unit (MPU)

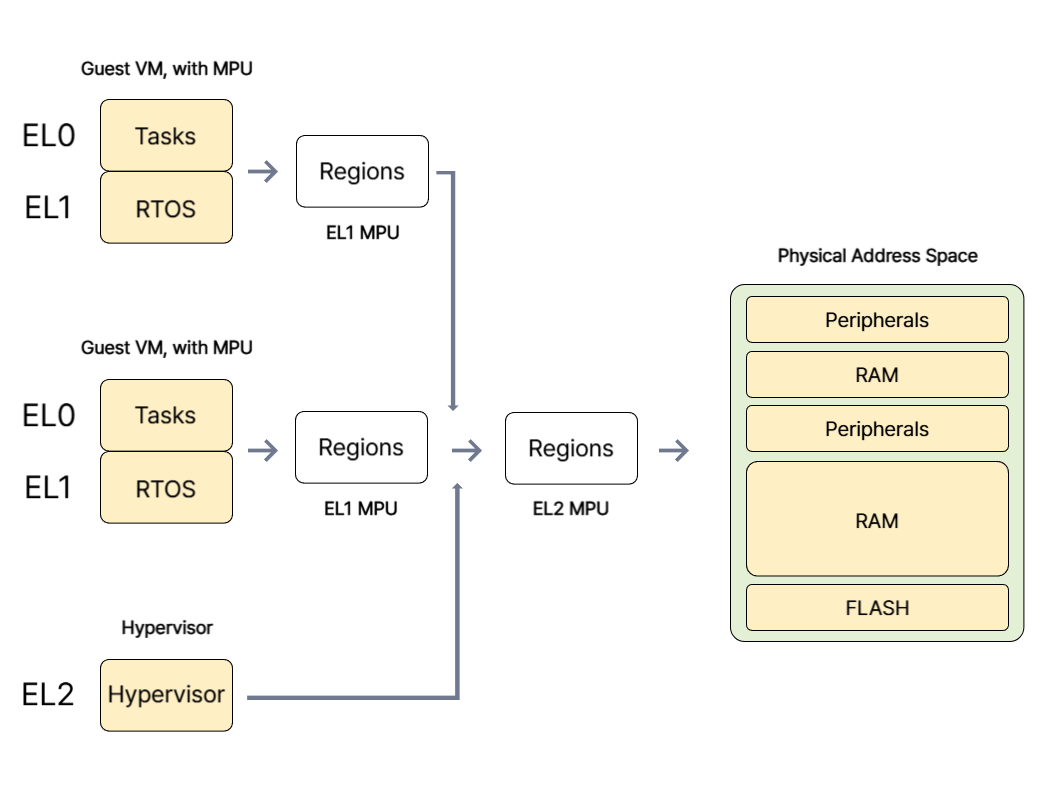

Armv8-R AArch32는 PMSA를 구현했기 때문에 메모리 보호를 위한 Stage1/Stage2 MPUs를 제공해요

pCPU 별로 EL1, EL2 용 MPU가 존재하는거에요

이를 Two stage memory protection이라고 부르죠

- Stage1 MPU 설정은 VM 내 RTOS(Guest OS)가 해요, VM 내부 Task가 메모리 자원에 접근할 때 올바른지 확인하죠

- Stage2 MPU 설정은 Hypervisor가 해요, VM 자체가 메모리 Region에 올바르게 접근했는지 확인해요

MPU 설정은 pCPU 별 register 설정을 통해 할 수 있어요

- EL1 MPU register는 EL1에서 접근 가능하죠

- EL2 MPU register는 EL2에서 접근 가능해요

- 각 Region 마다 Base와 Limit를 기준으로 메모리 구간을 정의하고, R/W권한·실행금지·메모리속성·캐시·쉐어 속성을 설정 해요

Stage1 : Guest OS 내 Task 간 메모리 보호

Guest OS(EL1)는 Task를 생성할 때, 각 Task에 대한 MPU Region 설정 정보를 정적으로 구성해둬요

vCPU위에서 특정 Task가 실행되면 Guest OS는 해당 Task의 mpu region 정보를 pCPU의 mpu register에 설정해요

만약 Task 전환(context switching)이 발생하면 다음 Task의 mpu region 정보를 pCPU의 mpu register에 덮어씌우죠

Stage2 : VM 간 메모리 보호

Hypervisor(EL2)가 각 VM이 시스템 전체 물리 메모리 중 허용된 영역만 접근하도록 제한해

ARMv8-R 아키텍처는 표준 Stage-2 MMU 대신 MPU 기반 보호를 사용하며, Hypervisor는 VM마다 접근 가능한 메모리 영역 정보를 소프트웨어적으로(또는 벤더 확장을 통해) 관리해요

같은 VM 내 vCPU들은 동일한 Stage-2 MPU 영역 구성을 공유하며, 이 설정은 소프트웨어에서 Context 형태로 유지하는거죠

즉, Hypervisor는 vCPU가 스케줄링될 때 해당 VM의 MPU Context를 pCPU의 하드웨어 MPU 레지스터에 실시간으로 로드하여 시스템 메모리 보호를 수행 하는거에요

Armv8-R AArch32는 Armv8-R AArch64와 달리 MMU나 VMSA는 없고 오직 MPU만 있어요

(MMU는 가상 주소 변환 과정 때문에 overhead가 크니 latency 만족이 까다롭죠)

Generic Interrupt Controller (GIC)

Interrupt를 처리하는 Generic Interrupt Controllers(GIC)는 GICv3 Architecture를 사용해요

Reference

모두 Arm 공식 Document에서 발췌한 내용이에요

https://developer.arm.com/documentation/DEN0130/0100/Armv8-R-AArch32?lang=en

https://developer.arm.com/documentation/109997/100/The-Memory-Protection-Unit?lang=en

'TIL > 2025' 카테고리의 다른 글

| About the Arm architecture (0) | 2025.04.28 |

|---|---|

| Arm R-Profile Architecture 학습 방법 및 자료 (0) | 2025.04.28 |

| 나만의 C++ 문자열 클래스 만들기, GuString (0) | 2025.04.24 |

| assembly 파일 분석 방법 (1) | 2025.04.24 |

| 멀티코어 환경 section offset 기반 복사 & 재매핑 패턴 (0) | 2025.04.24 |