📢 Hypervisor의 trap & emulate 과정에 대해 알아봐요

Trapping and emulation of instructions

Hypervisor는 VM의 특정 동작(예: 전력 관리)을 Trap해서 Emulation할 수 있어요

Trap이 설정되면 VM이 특정 동작(레지스터 접근, WFI 실행 등)을 할 때 예외가 발생하고, Hypervisor가 제어권을 가져옵니다.

예를 들어,

- HCR_EL2.TWI 비트 필드를 1로 설정하면

- VM(EL1/EL0)이 WFI 명령을 실행할 때 CPU 저전력 전환 대신 Hypervisor로 Trap(Exception)이 발생해요

Hypervisor는 이를 이용해

- CPU를 저전력으로 보내는 대신,

- 다른 vCPU를 스케줄링할 수 있어요

이런 Trap 메커니즘은 VM 간 격리와 시스템 안정성을 지키는 데 필수적입니다.

+----------+ +----------+

| vCPU0 | | vCPU1 |

| WFI | | |

+----------+ +----------+

| ^

| (1) | (2)

| Trap due to | ERET

| HCR_EL2.TWI |

+------|--------------------------|-------+

| v Hypervisor | |

| +-----------------------------+ |

| | Context Switcher | |

| +-----------------------------+ |

+-----------------------------------------+

Trap 사용처를 알아봐요

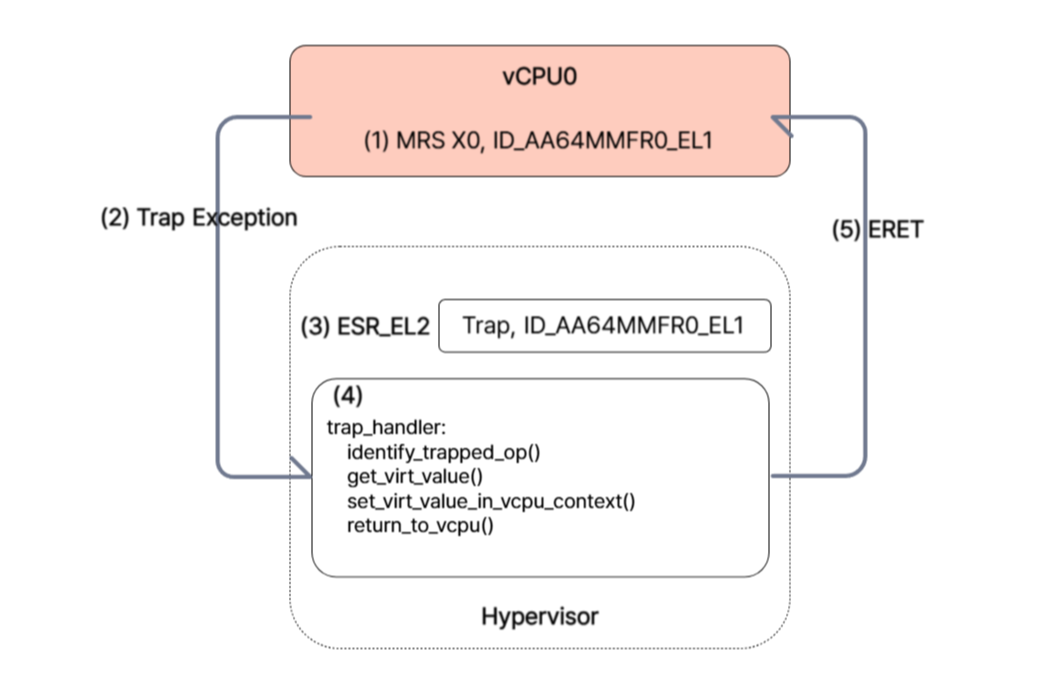

레지스터 가상 값 제공하기 (Presenting virtual values of registers)

OS는 부팅 시 시스템 레지스터(ID_AA64MMFR0_EL1)를 읽어 프로세서의 지원 기능을 확인해요

Hypervisor는 Guest OS가 진짜 값을 알지 못하도록 가상(virtual) 값을 제공하죠

그래서 레지스터 읽기에 Trap을 걸고, Trap이 발생하면 가짜 값으로 응답해요

(1) Read a register (ID_AA64MMFR0_EL1) in the EL0/1

(2) Trap exception (VM Exit)

(3) Check Exception type, register name (ESR_EL2 : EL2에서 발생한 예외 진단 정보를 담고 있는 시스템 레지스터)

(4) Run a proper handler

(5) ERET (VM Entry)

하드웨어는 그대로 두고, Guest에게 다른 세상을 보여줄 수 있어요

Lazy Context Switching에 트랩 활용하기

- 보통 OS는 부팅 후 한 번 설정한 MMU 설정 레지스터(TTBR<n>_EL1, TCR_EL1, MAIR_EL1)를 거의 수정하지 않아요

- Hypervisor는 복원만 하고 저장(save)을 생략해 Context Switch 속도를 최적화 할 수 있죠

- 만약 Guest가 레지스터를 수정하려 하면, HCR_EL2.TVM Trap을 걸어 이를 감지하고 저장을 수행해요

빠른 처리를 하면서도 예외 상황은 놓치지 않는 최적화에요

Trap vs Routing 개념 구분

- Trap: 특정 행동(예: 레지스터 읽기/쓰기)을 하면 예외(Exception) 를 발생 시키는 것

- Routing: 발생한 예외를 어느 Exception Level(EL0~EL3) 로 보낼지 결정하는 것

Trap은 "예외를 만들고", Routing은 "예외를 어디로 보낼지"를 결정해요

그러나 Trap은 무거운 작업

MIDR, MPIDR라는 두 레지스터가 있어요

OS가 CPU 정보를 확인하는 매우 빈번히 불리는 레지스터죠

자주 읽히기 때문에, 읽을 때마다 Trap 걸리면 성능이 느려져요

해결책: Trap 없이 가상 값을 주는 방법 사용!

- Hypervisor가 부팅 시 VPIDR_EL2 (가짜 MIDR) VMPIDR_EL2 (가짜 MPIDR)를 미리 설정해요

- 그러면 Guest가 MIDR_EL1 / MPIDR_EL1을 읽을 때 Trap 없이 가짜 값이 자동 반환 되죠

단, VPIDR_EL2, VMPIDR_EL2는 꼭 초기화가 필요해요 (Reset 후 값 없음)

Reference

https://developer.arm.com/documentation/102142/0100/Trapping-and-emulation-of-instructions

Documentation – Arm Developer

developer.arm.com

'TIL > 2025' 카테고리의 다른 글

| Virtualizing the generic timers, Arm architecture aarch64 (0) | 2025.04.29 |

|---|---|

| Virtualizing Exceptions in the Arm Architecture AArch64 (0) | 2025.04.29 |

| Memory Management Unit (MMU)의 Stage 2 translation (0) | 2025.04.29 |

| 가상화(Virtualization) 소개 | hypervisor, arm architecture (0) | 2025.04.28 |

| About the Arm architecture (0) | 2025.04.28 |